简介

- 核心功能 (Core Functionality)

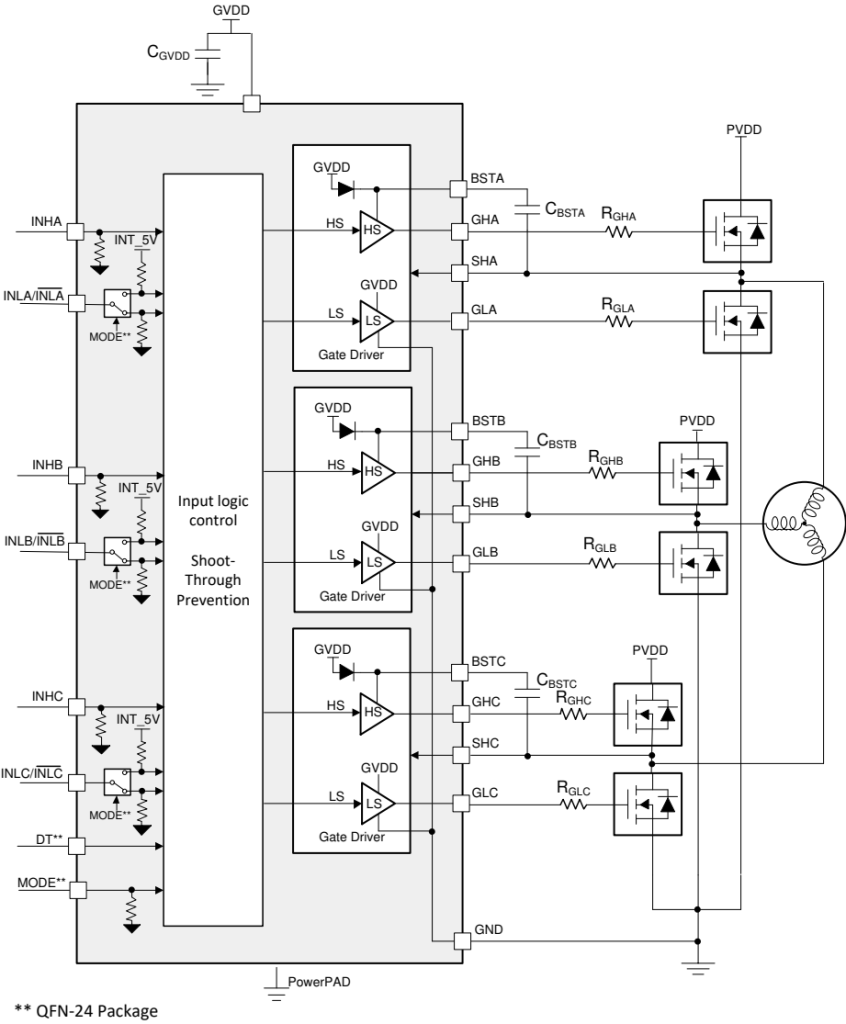

- 三相独立半桥栅极驱动器,可驱动6个外部N沟道功率MOSFET(每相高侧和低侧各1个)。

- 支持自举架构【1】(DRV8300D集成自举二极管,DRV8300N需外部二极管),生成高侧栅极驱动电压。

- 内置交叉导通预防逻辑【2】,确保高侧和低侧MOSFET不会同时导通(避免直通)。

- 工作电压范围 (Operating Supply Voltage Range)

- 低侧供电 (GVDD):5.0 V至20 V(推荐),绝对最大21.5 V。

- 高侧浮动电压 (BSTx):与SHx引脚相关,支持高达105 V工作电压(BSTx-SHx = 5–20 V),绝对最大125 V。

- 相位引脚 (SHx):耐受-22 V瞬态负压和85 V正压,提高系统鲁棒性【3】。

- 控制接口选项 (Control Interface Options)

- 独立高/低侧输入(INHx和INLx),支持3.3 V/5 V逻辑电平(绝对最大20 V)。

- MODE引脚 (仅QFN24):控制低侧输出极性(浮空时同相,接GVDD时反相)。

- DT引脚 (仅QFN24):通过外部电阻调节死区时间【4】(200 ns至2000 ns),固定封装(TSSOP20)内置200 ns死区。

- 输入内置下拉电阻(典型200 kΩ),防止浮空输入误触发。

- 栅极驱动能力 (Gate Drive Capability)

- 峰值输出电流【5】:高侧源电流【6】750 mA(最小400 mA),灌电流【7】1.5 A(最小850 mA);低侧源电流750 mA,灌电流1.5 A。

- 驱动架构:优化传播延迟【8】(典型125 ns),减少死区要求,提升效率。

- 逻辑输入支持 (Logic Input Support)

- 兼容3.3 V/5 V CMOS/TTL电平,高电平阈值≥2.7 V,低电平阈值≤0.8 V。

- 输入电流:高电平输入时典型20 μA(VIN = 5 V),低电平时≤1 μA(VIN = 0 V)。

- 保护特性 (Protection Features)

- 欠压保护 (UVLO):GVDD欠压锁定【9】(上升阈值4.6 V,下降阈值4.35 V);BST欠压锁定(上升阈值4.2 V,下降阈值4.0 V)。

- 死区时间:内置固定或可调死区(200 ns典型),防止高/低侧直通。

- 瞬态耐受:SHx引脚支持-22 V负压瞬变,GHx引脚支持125 V正压瞬变。

- 热保护:结温【10】范围-40°C至150°C,推荐工作环境-40°C至125°C。

- 动态性能【11】 (Dynamic Performance)

- 传播延迟:输入到输出典型125 ns(最大180 ns),匹配延迟【12】±4 ns。

- 开关时间:上升/下降时间【13】典型12 ns(CL = 1000 pF),最小输入脉冲宽度【14】70 ns。

- 死区调节:DT引脚外接电阻可线性调节死区(40 kΩ时200 ns,400 kΩ时2000 ns)。

- 封装选项 (Package Options)

- TSSOP20封装:尺寸6.40 mm × 4.40 mm,热阻【15】RθJA = 97.4°C/W。

- QFN24封装:尺寸4.00 mm × 4.00 mm,带散热焊盘,热阻RθJA = 49.3°C/W。

- 封装选择影响功能:QFN24支持MODE/DT引脚,TSSOP20固定死区和极性。

- 应用场景 (Application Scenarios)

- 高效电机驱动:电动自行车、踏板车、工业泵、伺服系统。

- 便携设备:无人机、园艺工具、真空吸尘器。

- 高可靠性系统:汽车电子(宽温支持)、物流机器人。

引脚详解

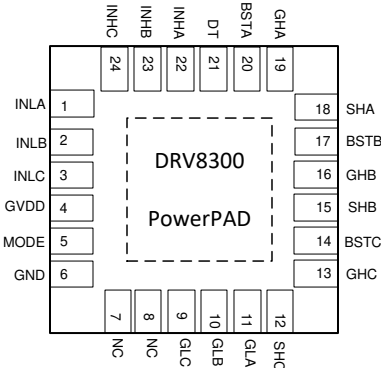

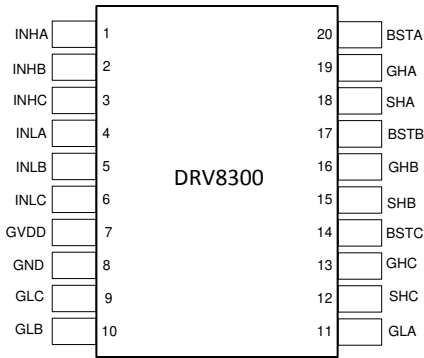

基于数据手册第6节,按功能分表详解TSSOP20和QFN24封装引脚。参数来自第7.5节,

测试条件:VGVDD = 12 V,无负载(除非注明)。

1. 控制输入引脚

| 功能描述 | TSSOP20引脚 | QFN24引脚 | 电气参数(典型值) |

|---|---|---|---|

| 高侧输入1 (INHA) | 1 | 22 | - 逻辑高阈值:≥2.7 V(VGVDD = 5 V) - 输入下拉电阻【16】:200 kΩ - 偏置电流【17】:20 μA(VIN = 5 V) |

| 高侧输入2 (INHB) | 2 | 23 | 同INHA |

| 高侧输入3 (INHC) | 3 | 24 | 同INHA |

| 低侧输入1 (INLA) | 4 | 1 | - 逻辑低阈值:≤0.8 V - 传输延迟:125 ns(上升沿) - 极性可调(MODE引脚控制) |

| 低侧输入2 (INLB) | 5 | 2 | 同INLA |

| 低侧输入3 (INLC) | 6 | 3 | 同INLA |

| MODE输入 (仅QFN24) | - | 5 | - 浮空:INLx同相输出 - 接GVDD:INLx反相输出 - 下拉电阻:200 kΩ |

| DT输入 (仅QFN24) | - | 21 | - 外接电阻调节死区(40–400 kΩ) - 浮空时固定200 ns死区 |

2. 电源与接地引脚

| 功能描述 | TSSOP20引脚 | QFN24引脚 | 电气参数 |

|---|---|---|---|

| 低侧供电 (GVDD) | 7 | 4 | - 工作范围:5.0–20 V - UVLO跳闸:上升4.6 V,下降4.35 V - 静态电流【18】:330 μA(无负载) |

| 系统接地 (GND) | 8 | 6 | 所有电压基准点,需低阻抗连接 |

| 高侧浮动供电1 (BSTA) | 20 | 20 | - 工作电压:BST-SH = 5–20 V - 绝对耐压:125 V - 漏电流【19】:<55 μA |

| 高侧浮动供电2 (BSTB) | 17 | 17 | 同BSTA |

| 高侧浮动供电3 (BSTC) | 14 | 14 | 同BSTA |

3. 输出驱动引脚

| 功能描述 | TSSOP20引脚 | QFN24引脚 | 驱动参数(VGVDD = 12 V) |

|---|---|---|---|

| 低侧输出1 (GLA) | 11 | 11 | - 灌电流:-1.5 A(峰值) - 下降时间:12 ns(CL = 1000 pF) - VOL:0.3 V(Io = 100 mA) |

| 低侧输出2 (GLB) | 10 | 10 | 同GLA |

| 低侧输出3 (GLC) | 9 | 9 | 同GLA |

| 高侧输出1 (GHA) | 19 | 19 | - 源电流:+0.75 A(峰值) - 上升时间【20】:24 ns(CL = 1000 pF) - VOH:0.6 V(Io = 100 mA) |

| 高侧输出2 (GHB) | 16 | 16 | 同GHA |

| 高侧输出3 (GHC) | 13 | 13 | 同GHA |

| 高侧源极1 (SHA) | 18 | 18 | - 耐压:-22 V至110 V(瞬态) - 静态漏电流:<55 μA - 连接MOSFET源极 |

| 高侧源极2 (SHB) | 15 | 15 | 同SHA |

| 高侧源极3 (SHC) | 12 | 12 | 同SHA |

4. 其他引脚(仅QFN24)

| 功能描述 | QFN24引脚 | 说明 |

|---|---|---|

| 空脚 (NC) | 7, 8 | 无内部连接,禁止外部连接 |

补充参数

基于文档第7.5节和第7.6节,补充静态与动态参数。

测试条件:VGVDD = 12 V,TA = 25°C(除非注明)。

1. 静态电气参数

| 参数 | 符号 | 测试条件 | 最小值 | 典型值 | 最大值 | 单位 |

|---|---|---|---|---|---|---|

| 输入逻辑高阈值 | VIH | INHx/INLx输入 | - | 2.7 | - | V |

| 输入逻辑低阈值 | VIL | INHx/INLx输入 | - | - | 0.8 | V |

| GVDD UVLO跳闸电压 | VGVDDUV | 供电上升时 | 4.45 | 4.6 | 4.7 | V |

| GVDD UVLO复位电压 | - | 供电下降时 | 4.2 | 4.35 | 4.4 | V |

| BST UVLO跳闸电压 | VBSTUV | BST-SH电压上升时 | 3.6 | 4.2 | 4.8 | V |

| BST静态电流 | IQBS | 高侧驱动 | - | 180 | 270 | μA |

| GVDD静态电流 | IQCC | 低侧驱动 | - | 330 | 500 | μA |

| 输出高电平电压【21】 | VOH | Io = 100 mA | - | 0.6 | 0.9 | V |

| 输出低电平电压【22】 | VOL | Io = 100 mA | - | 0.3 | 0.45 | V |

| 高侧输出短路电流【23】 | IOH | 脉冲宽度≤10 μs | 1.1 | 1.5 | 1.9 | A |

| 低侧输出短路电流 | IOL | 脉冲宽度≤10 μs | 1.3 | 1.8 | 2.3 | A |

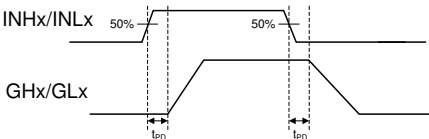

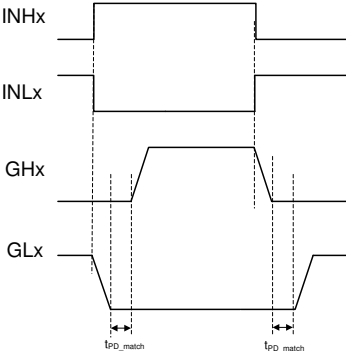

2. 动态电气参数

| 参数 | 符号 | 测试条件 | 最小值 | 典型值 | 最大值 | 单位 |

|---|---|---|---|---|---|---|

| 传播延迟(上升沿) | tPD_rise | INHx到GHx,无负载 | 70 | 125 | 180 | ns |

| 传播延迟(下降沿) | tPD_fall | INLx到GLx,无负载 | 70 | 125 | 180 | ns |

| 匹配延迟(同相) | tPD_match | GHx关断到GLx开启 | -30 | ±4 | 30 | ns |

| 上升时间 | tR | CL = 1000 pF | 10 | 24 | 50 | ns |

| 下降时间 | tF | CL = 1000 pF | 5 | 12 | 30 | ns |

| 死区时间(固定) | tDEAD | DT引脚浮空 | 150 | 215 | 280 | ns |

| 最小输入脉冲宽度 | tPW_MIN | INHx/INLx有效信号 | 40 | 70 | 150 | ns |

功能补充

- 直通防止功能:当高侧输入和低侧输入同时高电平时,输出强制关断,避免MOSFET直通。死区时间内确保高侧完全关断后低侧开启。

- 死区调节机制:QFN24封装通过DT引脚外接电阻(R_DT)调节死区,

公式:R_DT (kΩ) = Deadtime (ns) / 5。

设计参考

- 电源与接地设计

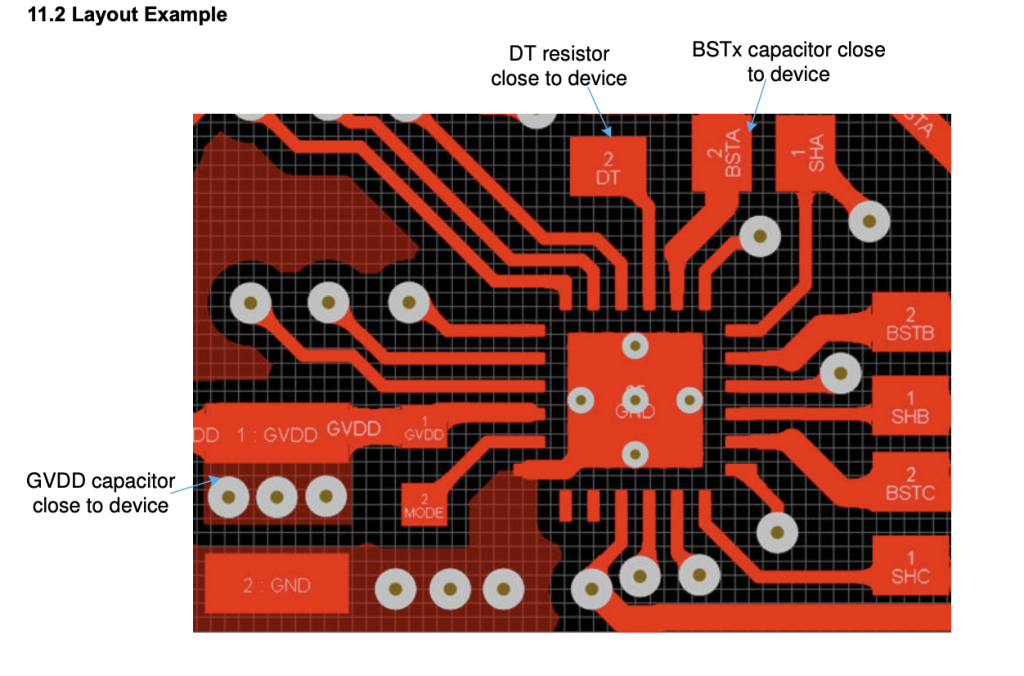

- GVDD滤波电容【24】 (C_GVDD):

- 选型:≥10 μF陶瓷电容(X5R/X7R),低ESR(<100 mΩ),耐压≥2×GVDD(如25 V)。

- 布局:紧邻GVDD和GND引脚(距离<5 mm),并联0.1 μF高频电容【25】,减少电源环路电感【26】。

- 系统接地 (GND):

- 星型接地【27】设计,单点连接功率地【28】(MOSFET源极)和信号地【29】(控制器)。

- QFN24封装底部散热焊盘必须全连接至地平面,作为主要散热路径。

- GVDD滤波电容【24】 (C_GVDD):

- 自举电路设计(高侧驱动)

- 自举二极管 (D_BOOT):

- DRV8300D内置,DRV8300N需外接快恢复二极管【30】(trr < 50 ns),反向耐压>125 V。

- 自举电容【31】 (C_BOOT):

- 选型:0.1–1 μF陶瓷电容(耐压>20 V),

公式:C_BOOT_MIN = Q_TOT / ΔV_BST(Q_TOT = MOSFET栅电荷【32】 + 漏电流积分【33】)。 - 布局:紧邻BSTx和SHx引脚,避免长走线引入电感(9.2.2节)。

- 注意:VBST-SH电压需保持在5–20 V范围,否则触发UVLO。

- 选型:0.1–1 μF陶瓷电容(耐压>20 V),

- 自举二极管 (D_BOOT):

- 输出级设计

- 栅极电阻【34】 (R_GATE):

- 选型:基于死区时间和MOSFET栅电荷(Qg)计算,

确保R_GATE × Qg ≤ tDEAD(如Qg=48 nC时,R_GATE≤4 Ω)。 - 作用:控制开关速度【35】,减少振荡;过大延长开关时间,过小导致过冲【36】。

- 选型:基于死区时间和MOSFET栅电荷(Qg)计算,

- 栅源电阻【37】 (R_GS):

- 选型:10–100 kΩ,用于泄放MOSFET栅极电荷,防止误触发。

- 布局:直接连接MOSFET栅极和源极,路径最短化(<10 mm)。

- 栅极电阻【34】 (R_GATE):

- 布局技巧

- 引脚走线:

- HO/LO输出线宽≥12 mil(0.3 mm),减少电感;避免平行于高电流路径(如MOSFET漏极)。

- INHx/INLx输入走线短直,加地线屏蔽,减少噪声耦合。

- 热管理【38】:

- TSSOP20封装:热阻RθJA = 97.4°C/W,建议顶层铺铜【39】(≥2 oz)或加散热片。

- QFN24封装:热阻RθJA = 49.3°C/W,底部焊盘需通过过孔连接至内部地平面。

- 元件放置:

- 所有电容(C_GVDD, C_BOOT)紧邻芯片,减少寄生电感【40】。

- 栅极电阻使用金属膜类型(低电感),测试点添加于HO/LO和INHx/INLx,方便示波器调试开关波形。

- 引脚走线:

- 注意事项

- 死区时间受PCB寄生参数【41】(如走线电感)影响,实测验证关键时序。

- 高频应用(>100 kHz)时,使用四层板【42】分离功率/信号层,参考官方Layout示例【43】。

Comments NOTHING