AI 摘要

SN74HC125:四路独立三态缓冲,支持2-6V宽电压兼容,输出可控高阻态。适用于总线共享与信号隔离,性能稳定,设计灵活。

简介

核心功能

- 四路独立三态缓冲器【1】:每路执行布尔函数 Y=A(正逻辑),输出支持高阻态(Z)控制。

- 三态输出【2】:通过使能引脚(OE)控制输出状态(高/低电平或高阻),适用于总线共享和信号隔离场景。

- 宽电压支持【3】:工作电压范围 2V 至 6V,兼容 TTL/CMOS 电平。

核心参数速查总表

| 参数类别 | 符号 | 测试条件 | 最小值 | 典型值 | 最大值 | 单位 |

|---|

| 工作电压范围 | VCC | - | 2.0 | 5.0 | 6.0 | V |

| 静态电流【4】 | ICC | VCC=6V | - | 8 | 80 | μA |

| 输入电容【5】 | Ci | - | - | 3 | 10 | pF |

| 工作温度【6】 | TA | - | -40 | - | 85 | °C |

| 高电平输入阈值【7】 | VIH | VCC=4.5V | 3.15 | - | - | V |

| 低电平输入阈值【8】 | VIL | VCC=4.5V | - | - | 1.35 | V |

| 输入漏电流【9】 | II | VI=Vcc【10】/0V | - | - | ±1 | μA |

| 高电平输出电压【11】 | VOH | IOH=−6mA | 3.84 | 4.3 | - | V |

| 低电平输出电压【12】 | VOL | IOL=6mA | - | 0.26 | 0.33 | V |

| 三态漏电流【13】 | IOZ | VO=VCC/0V | - | 0.5 | 5 | μA |

| 传播延迟【14】 | tpd | CL=50pF | - | 24 | 36 | ns |

| 上升时间【15】 | tr | CL=50pF | - | 12 | 18 | ns |

| 下降时间【16】 | tf | CL=50pF | - | 12 | 18 | ns |

| 电源耐受电压【17】 | - | - | -0.5 | - | 7.0 | V |

| 输出耐受电流【18】 | - | - | - | - | ±35 | mA |

| 结温上限【19】 | TJ | - | - | - | 150 | °C |

| 驱动电流【20】 | IO | 连续输出 | - | - | ±35 | mA |

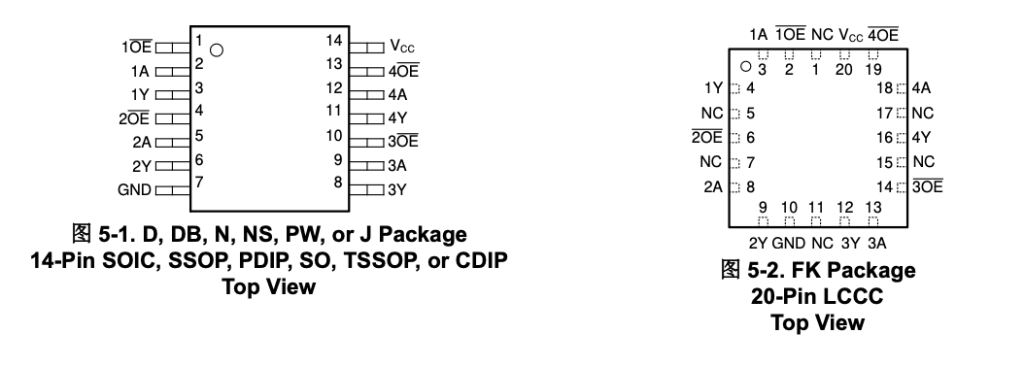

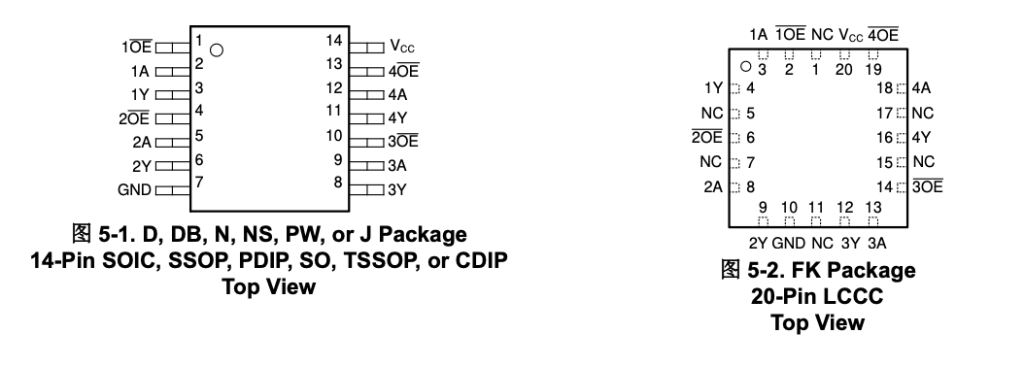

引脚详解

| 封装型号 | 封装尺寸 | 引脚数 | 热阻【21】 RθJA (°C/W) |

|---|

| SOIC【22】 (D) | 8.70mm × 3.90mm | 14 | 133.6 |

| SSOP【23】 (DB) | 6.50mm × 5.30mm | 14 | 108.0 |

| PDIP【24】 (N) | 19.30mm × 6.40mm | 14 | 63.0 |

| TSSOP【25】 (PW) | 5.00mm × 4.40mm | 14 | 151.7 |

| LCCC【26】 (FK) | 8.90mm × 8.90mm | 20 | 非适用(军用级) |

控制输入引脚

| 功能描述 | 引脚名 | SOIC/SSOP/TSSOP引脚 | LCCC引脚 | 电气参数(典型值) |

|---|

| 通道1输出使能(低有效) | 1OE【27】 | 1 | 2 | 输入电流 ≤1μA |

| 通道1输入 | 1A【28】 | 2 | 3 | VIH=1.5V (2V) |

| 通道2输出使能(低有效) | 2OE【29】 | 4 | 6 | 同 1OE |

| 通道2输入 | 2A【30】 | 5 | 8 | VIL=0.5V (2V) |

电源与接地引脚

| 功能描述 | 引脚名 | SOIC/SSOP/TSSOP引脚 | LCCC引脚 | 电气参数 |

|---|

| 电源正极 | Vcc | 14 | 20 | 工作范围 2-6V |

| 接地 | GND【31】 | 7 | 10 | 基准电位点 |

输出引脚

| 功能描述 | 引脚名 | SOIC/SSOP/TSSOP引脚 | LCCC引脚 | 驱动能力(VCC=4.5V) |

|---|

| 通道1输出 | 1Y【32】 | 3 | 4 | IOL=6mA (VOL=0.26V) |

| 通道2输出 | 2Y【33】 | 6 | 9 | 同 1Y |

2.3 引脚电参数

| 参数 | 符号 | 测试条件 | 最小值 | 典型值 | 最大值 | 单位 |

|---|

| 高电平输入电压 | VIH | VCC=2V | 1.5 | - | - | V |

| 低电平输入电压 | VIL | VCC=2V | - | - | 0.5 | V |

| 输出漏电流(高阻态) | IOZ | VO=VCC/0V | - | 0.5 | 5 | μA |

参数补充

静态电气特性

| 参数 | 符号 | 测试条件 | VCC=4.5V 典型值 |

|---|

| 输出高电平电压 | VOH | IOH=−6mA | 4.3V |

| 输出低电平电压 | VOL | IOL=6mA | 0.26V |

| 输入电容 | Ci | - | 10pF |

动态性能

| 参数 | 符号 | 测试条件 (CL=50pF) | VCC=4.5V 最大值 |

|---|

| 传播延迟(A→Y) | tpd | - | 36ns |

| 输出使能时间 | ten | - | 36ns |

| 输出禁用时间 | tdis | - | 36ns |

| 上升/下降时间 | tr/tf | - | 18ns |

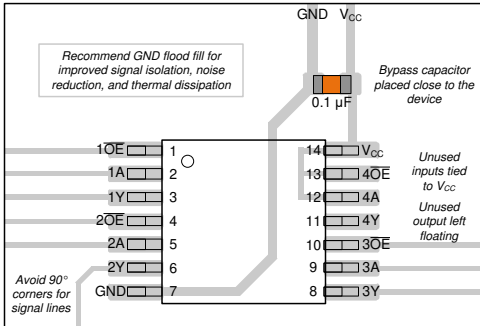

关键设计

- 未用输入处理【34】:

- 所有未用输入引脚必须接 VCC 或 GND,避免浮空引发振荡。

- 推荐使用 10kΩ 上拉/下拉电阻(默认高电平或低电平)。

- 电源去耦【35】:

- VCC 与 GND 间并联 0.1μF 陶瓷电容【36】(靠近芯片引脚),抑制高频噪声。

- 可选:增加 1μF 钽电容【37】增强低频稳定性。

- 输出端设计:

- 输出走线宽度 ≥8mil,减少电感效应。

- 避免直接连接 VCC/GND,防止过流损坏。

热管理设计

| 封装类型 | 热阻 RθJA | 散热建议 |

|---|

| TSSOP (PW) | 151.7°C/W | 增加底部铜箔散热面积 |

| PDIP (N) | 63.0°C/W | 无需额外散热(低功耗场景) |

抗干扰设计

- 输入信号:

- 走线短直,避免与功率线平行。

- 敏感信号线用地线屏蔽。

- 高阻态控制:

- OE 信号线加 RC 滤波器(R=100Ω, C=100pF),抑制使能瞬态噪声。

应用注意事项

- 负载电容限制【38】:

- 最大负载电容 CL≤70pF(确保信号完整性)。

- 若需驱动更大容性负载,串联 22-100Ω 电阻限流。

- ESD 防护:

- 人体模型(HBM)防护:±2000V。

- 操作时需佩戴防静电手环。

- 时序验证【39】:

- 实际传输延迟受 PCB 寄生参数影响,建议用示波器测试关键路径(如 A→Y 延时)。

实测提示:死区时间【40】、开关速度【41】等参数需通过原型板验证,参考数据手册第7节测试电路。

Comments NOTHING