简介

1.核心功能:

- 超低噪声与高压差抑制:输出噪声电压【1】典型值仅30μV RMS,电源抑制比(PSRR)达-50dB @10kHz,适合噪声敏感应用(如CDMA/GSM手机)。

- 节能设计:静态电流【2】低至25μA(典型值),关断模式电流【3】仅0.7μA,显著延长电池寿命。

- 小型化与简化设计:支持低ESR陶瓷电容(仅需1μF输出电容),无需额外旁路电容【4】,节省PCB空间。

- 快速响应:开启时间【5】小于40μs,支持高频负载瞬变【6】。

- 应用场景:笔记本电脑、手持仪器、Mini PCIe卡等便携设备。

- 封装选项:提供SC-82、SOT-23-5、SC-70-5和WDFN-6L 2x2封装,均符合RoHS标准,兼容无铅焊接工艺【7】。

2.核心参数速查表:

以下表格提炼自数据手册关键指标,按功能分类呈现,支持快速选型与设计验证:

| 参数类别 | 参数名称 | 符号 | 典型值 | 测试条件 | 单位 |

|---|---|---|---|---|---|

| 输入特性 | 输入电压范围 | VIN | 2.2 ~ 5.5 | - | V |

| 输出噪声 | 输出噪声电压 | Vn | 30 | VOUT=1.5V, IOUT=0mA, 带宽10Hz~100kHz | μV RMS |

| 静态功耗 | 静态电流 | IQ | 25 | VEN=5V, IOUT=0mA | μA |

| 关断电流 | ISHDN | 0.7 | VEN=0V | μA | |

| 压降特性 | 压降电压【8】(满载) | VDROP | 250 | IOUT=500mA, 2.7V≤VIN≤5.5V | mV |

| 精度控制 | 输出电压精度 | ΔVOUT | ±2% | IOUT=10mA | % |

| 动态性能 | 电源抑制比 | PSRR | 50 | IOUT=100mA, f=10kHz | dB |

| 启动时间 | tON | 40 | - | μs | |

| 保护特性 | 限流保护 | ILIM | 0.6 | RLOAD=0Ω, 2.7V≤VIN≤5.5V | A |

| 热关断【9】温度 | TSD | 170 | 触发保护阈值 | °C | |

| 热设计 | 热阻(WDFN-6L 2x2封装) | θJA | 165 | JEDEC 51-3单层板 | °C/W |

| 热阻(SOT-23-5封装) | θJA | 250 | JEDEC 51-3单层板 | °C/W |

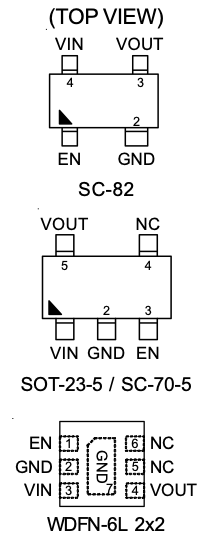

引脚说明

| 引脚名称 | 引脚编号(SC-82) | 引脚编号(SOT-23-5/SC-70-5) | 引脚编号(WDFN-6L 2x2) | 功能描述 | 关键参数(来自电气特性) |

|---|---|---|---|---|---|

| VOUT | 3 | 5 | 4 | 稳压器输出端 | 输出电压精度:±2%(@10mA) |

| GND | 2 | 2 | 2, 7(裸露焊盘) | 接地端 | 必须焊接至大面积PCB铺铜以散热 |

| EN | 1 | 3 | 1 | 使能控制端(高电平激活) | 逻辑低阈值(VIL):<0.6V;逻辑高阈值(VIH):>1.6V; 使能引脚电流(IEN):最大1μA |

| VIN | 4 | 1 | 3 | 电源输入端 | 输入电压范围:2.2V–5.5V |

| NC | — | 4 | 5,6 | 无内部连接 | 无需外部电路 |

参数说明:

- EN引脚:逻辑高电平(>1.6V)时启动稳压器,逻辑低电平(<0.6V)时进入关断模式(功耗0.7μA)。不可悬空。

- GND引脚:WDFN封装的裸露焊盘(Pin 7)需连接PCB铺铜以优化散热,否则影响最大功耗【10】(见设计参考部分)。

- VIN/VOUT参数:压差电压(V_DROP)典型值250mV @500mA(VIN≥2.7V),确保高效能量转换。

其他参数

除引脚参数外,关键特性分为电气性能、保护机制和热特性三类:

1. 电气性能

| 参数 | 符号 | 测试条件 | 最小值 | 典型值 | 最大值 | 单位 |

|---|---|---|---|---|---|---|

| 输出噪声电压 | VON | VOUT=1.5V, IOUT=0mA | — | 30 | — | μV RMS |

| 负载调整率【11】 | ΔVLOAD | 1mA<IOUT<500mA (VIN≥2.7V) | — | — | 1% | % |

| 线性调整率【12】 | ΔVLINE | VIN=(VOUT+0.5V)至5.5V | — | 0.01 | 0.2 | %/V |

| 静态电流 | IQ | VEN=5V, IOUT=0mA | — | 25 | 50 | μA |

| 电流限制【13】 | ILIM | RLOAD=0Ω, VIN≥2.7V | 0.5 | 0.6 | 0.85 | A |

2. 保护机制

| 参数 | 符号 | 典型值 | 单位 | 功能 |

|---|---|---|---|---|

| 热关断温度 | TSD | 170 | °C | 结温超限时关闭输出 |

| 热关断迟滞【14】 | ΔTSD | 30 | °C | 温度降低30°C后自动恢复 |

| 电流限制 | ILIM | 0.6 | A | 输出短路保护(可无限时短路至GND) |

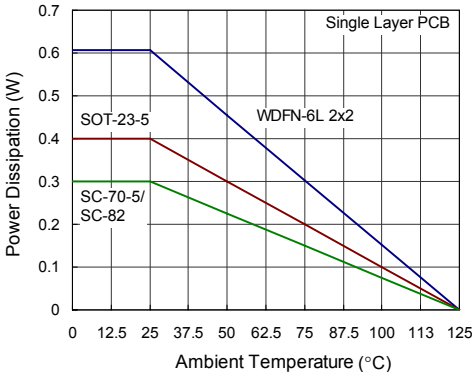

3. 热特性

| 参数 | 符号 | SC-82封装 | SOT-23-5封装 | WDFN-6L 2x2封装 | 单位 |

|---|---|---|---|---|---|

| 结到环境热阻【15】 | θJA | 333 | 250 | 165 | °C/W |

| 最大功耗@TA=25°C | PD(MAX) | 0.300 | 0.400 | 0.606 | W |

| 存储温度范围 | TSTG | -65至150 | -65至150 | -65至150 | °C |

最大功耗公式:PD=(VIN−VOUT)×IOUT+VIN×IQ

温升限值公式:PD(MAX)=(TJ(MAX)−TA)/θJA(TJ(MAX)=125°C)

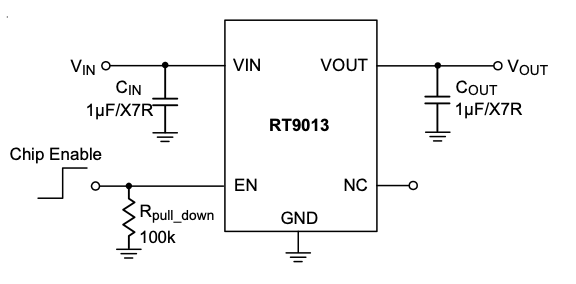

设计参考

1.电容选型

- 输入电容(CIN):

- 需≥1μF陶瓷电容(X7R),ESR无严格要求。

- 布局要求:距离VIN引脚≤0.5英寸,连接至纯净模拟地【16】。

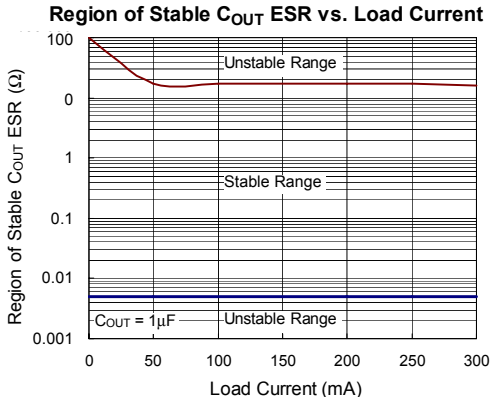

- 输出电容(COUT):

- 需≥1μF陶瓷电容(X7R),ESR≥5mΩ以确保稳定性【17】。

- 更大电容值可改善噪声和瞬态响应【18】(如PSRR)。

- 在数据手册中展示了允许的ESR范围随负载电流的变化

2. 使能控制设计

- EN引脚需直接连接逻辑电平(CMOS兼容【19】),禁止悬空,推荐添加下拉电阻【20】。

- 逻辑高电平(>1.6V)启动,逻辑低电平(<0.6V)关断,典型响应时间<40μs。

- 若需常开,可将EN引脚接至VIN。

3. 热设计

- 散热优化:WDFN封装的裸露焊盘(GND)必须焊接至大面积PCB铺铜。

- 功耗管理:环境温度(TA)升高时需降额使用。数据手册提供封装降额曲线【21】,避免超温关断:

Comments NOTHING