AI 摘要

LMR514X0:专为严苛工业场景打造的同步降压转换器,提供4-36V宽压输入与高达5A的持续输出。其高效能设计集成同步整流,并以极简外围(内部补偿)确保高可靠性与设计便捷性。

简介

- 宽压输入:4V–36V工作范围,适应工业严苛环境(如PLC、测试仪器)。

- 高输出电流:双版本支持4A(LMR51440)或5A(LMR51450)持续电流。

- 高效能设计:

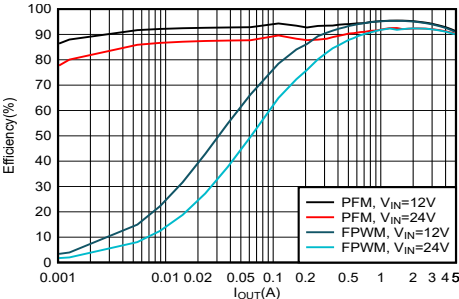

- 低静态电流(25μA),PFM版本轻载效率>90%

- 集成同步整流MOSFET(高侧78mΩ/低侧45mΩ)。

- 灵活频率控制:200kHz–1.1MHz可调(通过RT引脚电阻),支持频率扩展频谱(±10%)。

- 多重保护:逐周期限流、短路打嗝模式、热关断(160°C触发)。

- 简易设计:内部补偿,无需外部补偿电路。

核心参数速查表

| 参数类别 | 参数名称 | 符号 | 最小值 | 典型值 | 最大值 | 单位 | 条件 |

|---|

| 输入特性 | 输入电压范围 | VIN | 4 | - | 36 | V | - |

| 待机静态电流 | ISD | - | 3 | 6 | μA | VEN=0V |

| 输出特性 | 输出电流 | IOUT | - | 4/5 | - | A | LMR51440/LMR51450 |

| 反馈电压精度 | VFB | 0.792 | 0.8 | 0.808 | V | TJ=25°C |

| 开关特性 | 开关频率范围 | fSW | 200 | - | 1100 | kHz | RT调节 |

| 最小导通时间 | tON_MIN | - | 75 | - | ns | VIN=24V |

| 保护特性 | 高侧峰值限流 | ISC | 6.4 | 8 | 9.6 | A | LMR51450 |

| 热关断温度 | TSD | - | 160 | - | °C | 触发阈值 |

| 能效特性 | 非开关静态电流 | IQ | - | 25 | - | μA | PFM模式 |

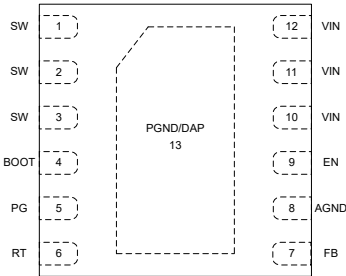

引脚详解

| 功能分类 | 引脚名 | WSON-12引脚号 | 电气特性 |

|---|

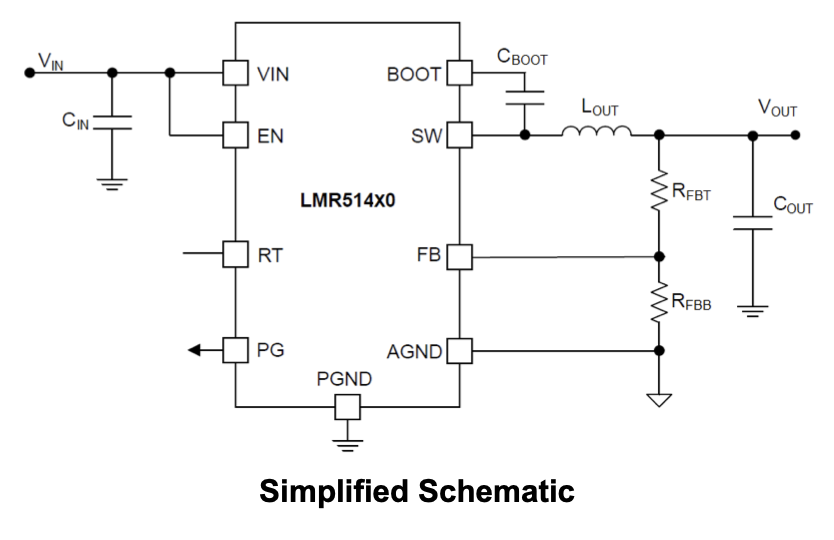

| 电源输入 | VIN | 10,11,12 | 输入电压范围:4–36V;需并联低ESR陶瓷电容(≥10μF),走线短直。 |

| 功率开关 | SW | 1,2,3 | 开关节点,连接电感;耐压瞬态40V(<10ns),持续耐压36V。 |

| 自举供电 | BOOT | 4 | 高侧驱动供电,需接100nF陶瓷电容至SW引脚;电压限制:BOOT-SW ≤5.5V。 |

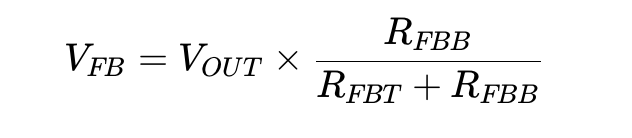

| 反馈控制 | FB | 7 | 反馈输入,接电阻分压网络

(RFBT=100kΩ, RFBB=19.1kΩ@VOUT=5V)。 |

| 频率配置 | RT | 6 | 频率设置引脚:悬空=500kHz,接地=1MHz,电阻调节范围14.3kΩ–84.5kΩ。 |

| 使能控制 | EN | 9 | 精密使能输入:高电平>1.4V启动,低电平<0.8V关闭;支持电阻分压UVLO设置。 |

| 电源良好指示 | PG | 5 | 开漏输出,低有效(VOUT异常时拉低);需外接10k–100kΩ上拉电阻。 |

| 接地 | PGND | 13 | 功率地,连接输入/输出电容地端;低阻抗铺铜。 |

| AGND | 8 | 模拟地,通过短线连接PGND。 |

补充参数

反馈电阻选择

| VOUT(V) | RFBT(kΩ) | RFBB(kΩ) | 最接近标准值 (E96系列) | 实际 VOUT误差 |

|---|

| 3.3 | 100 | 32.0 | 32.4k (1%) | +0.12% |

| 5.0 | 100 | 19.05 | 19.1k (1%) | +0.03% |

| 9.0 | 100 | 9.76 | 9.76k (1%) | +0.02% |

| 12.0 | 100 | 7.27 | 7.32k (1%) | -0.15% |

| 16.0 | 100 | 5.33 | 5.36k (1%) | -0.12% |

| 24.0 | 100 | 3.48 | 3.48k (1%) | +0.05% |

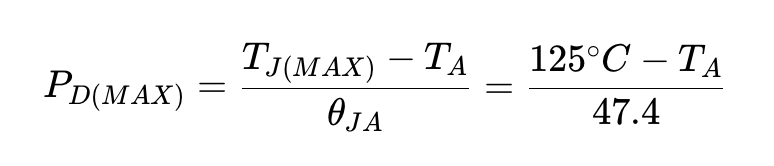

热设计参数

- 结到环境热阻:θJA = 47.4°C/W(无散热器),θJC = 6.3°C/W(底部焊盘)。

- 最大功耗公式:示例:TA=85°C时,PD(MAX)≈0.84W(需优化散热)。

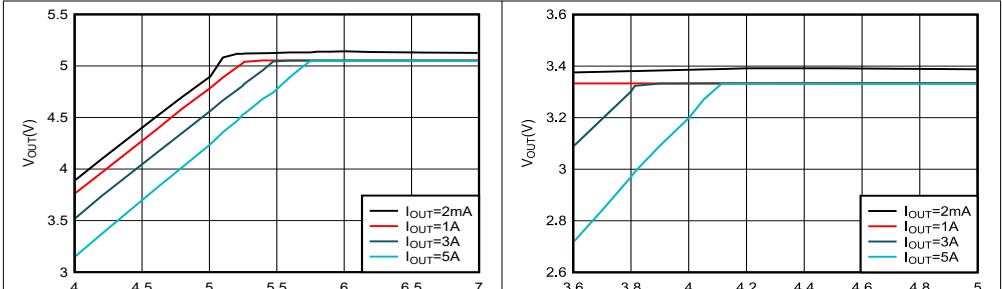

瞬态响应

- 负载调整率:±1.5%(IOUT=0→5A, VOUT=5V)。

- 线性调整率:±0.5%(VIN=6–36V, IOUT=3A)。

- 软启动时间:3.2–7.2ms(内部固定)。

4.3 稳定性要求

- 最小输出电容:20μF(陶瓷电容,ESR<5mΩ)。

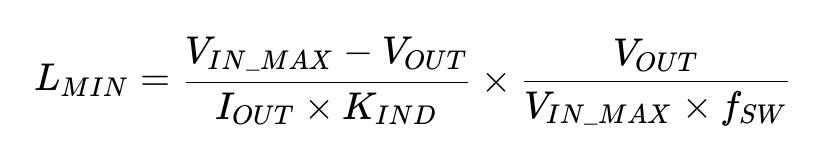

- 电感选择公式:

(KIND=0.4时,LMIN≈4.3μH@VIN=36V, VOUT=5V)

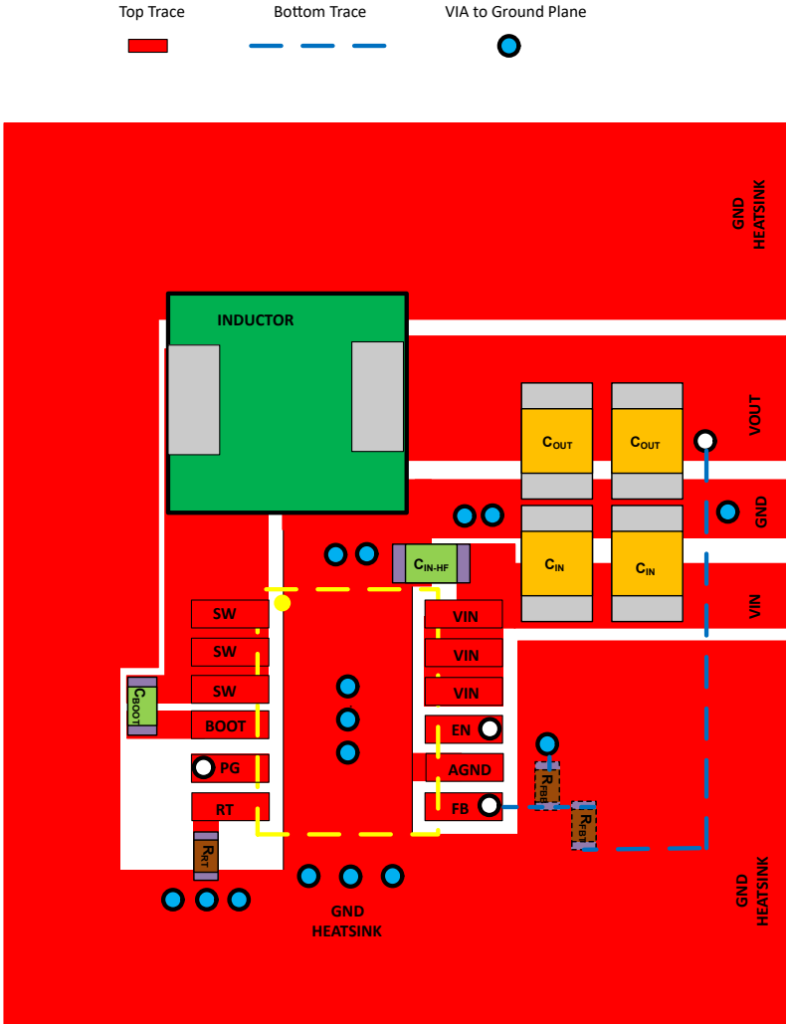

5. LAYOUT建议

关键设计准则

- 功率回路最小化:

- VIN电容(CIN)紧贴VIN/PGND引脚(距离≤3mm)。

- SW节点面积最小化,电感靠近SW引脚。

- 地平面设计:

- PGND与AGND通过独立短线连接,底层铺设完整地平面。

- 散热焊盘(底部EP)通过4×4过孔阵列(孔径≥0.3mm)连接底层地。

- 噪声敏感走线:

- FB分压电阻靠近FB引脚,走线远离SW和电感。

- EN信号加10kΩ下拉电阻,避免浮空。

热设计准则

- 铜箔面积:≥100mm²(底层)。

- 过孔设计:EP焊盘下方使用0.3mm孔径过孔,间距1mm。

- 温升估算:

- 双面PCB+过孔:θJA≈23°C/W(实测值),TA上限提升至105°C(@PD=0.84W)。

注意

- NC引脚:禁止布线(引脚6)。

- 输出电容ESR:>1Ω可能导致振荡,建议ESR<100mΩ。

Comments NOTHING